- An Empirical Formulation for Predicting the Thickness of Multilayer PCB

Nam-Hoon Kim*, Gwan-Hee Han*, Min-Su Lee**, Hyun-Ho Kim**, Kwang-Bok Shin*†

* Department of Mechanical Engineering, Hanbat National University

** Korea Packaging Integration Association- 다층 PCB의 두께 예측을 위한 실험식 도출 연구

김남훈* · 한관희* · 이민수** · 김현호** · 신광복*†

This article is an open access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/4.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

In this paper, the thickness of a multilayer PCB was predicted through an empirical formulation based on the physical properties of the prepreg used in multilayer PCB. Since the thickness of prepreg reduction when manufacturing a PCB due to the physical properties and copper foil residual rate, it is necessary to accurately predict the thickness of the PCB through the thickness empirical formulation. To determine the density of the prepreg, the mass and thickness of the prepreg were measured. To manufacture the CCL, the prepreg and copper foil were laminated using a hot press machine, and the thickness was measured using a microscope and micrometer. An 8-layerd PCB was designed with different circuit densities to measure the change in the thickness with the copper foil residual ratio, and the proposed empirical formulation was verified by comparing the measured thickness with the value obtained using the empirical formulation. As a result, the errors for the CCL and multilayer PCB were 2.56% and 4.48%, respectively, which demonstrated the reliability of the empirical formulation.

본 논문은 다층 PCB에 사용되는 프리프레그의 물성을 파악하여 제시한 두께 실험식을 통해 PCB의 두께를 예측하기 위한 연구를 수행하였다. 프리프레그는 물성과 동박 잔존율에 의해서 PCB 제작시 두께가 감소하기 때문에 두께 실험식을 통한 정확한 PCB의 두께 예측이 필요하다. 두께 실험식에 사용되는 프리프레그의 밀도를 파악하기 위해 질량 및 두께를 측정하여 밀도를 도출하였다. 이후 CCL을 제작하기 위해 프리프레그와 동박을 적층하여 핫 프레스기를 사용하였고 광학현미경과 마이크로미터를 사용하여 두께를 측정하였다. 또한 동박 잔존율에 따른 두께 변화를 측정하기 위해 회로밀도를 다르게 구성하여 8층 PCB를 설계하였고 두께 측정 결과와 두께 실험식으로 도출된 두께를 비교하여 두께 실험식을 검증하였다. 비교 결과 CCL의 경우 2.56%, 다층 PCB의 경우 4.48%의 오차를 보였고 이를 통해 두께실험식의 신뢰성을 확인하였다.

Keywords: 인쇄회로기판(Printed circuit board), 동박 적층판(Copper clad laminate), 두께 실험식(Thickness empirical formulation), 프리프레그(Prepreg)

최근 IT기술의 발전 및 휴대용 기기의 보급 확대로 인한 전자부품은 소형화, 경량화 그리고 고성능화 되는 추세이다. 전자기기의 소형화 및 경량화를 위해서는 기기에 사용되는 전자부품의 크기와 면적을 감소시켜야 하며, 고성능화를 위하여 높은 성능의 부품을 고밀도로 배치하여야 한다. 이에 따라 주요 부품인 PCB(Printed Circuit Board)의 두께도 얇아지며, 실장의 고밀도화가 이루어지고 있다[1]. 반도체 기술의 진보로 인하여 반도체 칩의 동작 속도는 크게 향상되었으나, 전기적으로 연결하는 PCB의 동작 속도가 이를 따라가지 못하여 높은 동작속도에서 병목현상을 일으키는 경우가 많다. 병목현상을 해결하기 위해 열변형 특성과 유전율의 변화가 적고 방열특성 및 기계적 물성이 높은 탄소섬유복합재 등의 다양한 신소재를 적용한 절연체로 제작된 PCB에 대한 연구가 진행중이다. 하지만 새롭게 개발되는 절연체를 적용하여 PCB를 제작하기 위해서는 절연체의 특성을 파악하여 설계가 이루어져야 하며, 정확한 설계식을 통한 체계적인 설계가 필요하다[2-5].

PCB 설계는 대부분 전기신호를 중점으로 설계하는 것이 일반적이지만, 전자기기의 소형화로 인해 기판 두께에 대한 설계도 중요시되고 있다. PCB는 절연층과 회로층이 반복되어 구성되기 때문에 층별 두께가 정확하게 설계되지 않으면 기판의 강도 및 강성 감소, 내부 반도체 칩 또는 땜납 접합부 등에 결함이 발생된다. 또한 고성능 전자부품의 고밀도 실장으로 발열량이 증가하여 층별 두께와 소재의 열탄성 계수 차이로 인해 기판의 굽힘 변형을 야기한다[6,7]. 이처럼 PCB의 두께는 기판의 내구성에 미치는 영향이 매우 크기 때문에 정확한 두께 설계는 필수적이다.

PCB 설계에 대한 국내 연구 사례로 Kim 등[8]은 유전체의 전기적 특성을 파악하고 회로 배선의 폭과 간격 등을 설계하여 신호 무결성을 개선하고 동작 속도를 높이는 연구를 수행하였으며, Lee 등[9]은 수치해석을 통해 PCB 기판의 휨을 최소로 하기 위한 더미 패턴을 최적 설계하는 방법을 고안하였다. 또한, Yoon 등[10]은 PCB 선로의 패턴에 따른 최적의 임피던스에 맞는 설계가 가능하도록 시뮬레이터를 구현하였다. 문헌 조사를 통해 알 수 있듯이, 기존 연구에서는 대부분 회로 설계와 PCB의 두께를 변경하여 PCB의 내구성 및 성능을 향상시키는 방향으로 연구가 진행되었으며, 성능 및 내구성 향상을 위해 정확한 PCB의 두께를 도출하는 방법에 대한 연구사례는 미비하다. 따라서, 다층 PCB의 경우 회로 밀도나 절연체의 특성에 따라 층별 두께가 변화할 수 있기 때문에 정확한 두께 설계가 필요하다.

본 논문은 다층 PCB에 사용되는 유리섬유/에폭시 프리프레그(Glass/Epoxy Prepreg)의 밀도와 동박 잔존율을 고려한 두께 예측 실험식을 이용하여 다층 PCB의 두께를 예측하기 위한 연구를 수행하였다. 프리프레그의 물성을 파악하기 위해 질량 및 두께를 측정하였고 밀도를 도출하였다. 프리프레그와 동박을 적층하여 CCL(Copper Clad Laminate)을 제작하였고 제작 장비로 핫 프레스기를 사용하였다. 제작된 CCL의 두께를 측정하기 위해 광학현미경과 마이크로미터를 사용하였다. 또한 동박 잔존율에 따른 두께 변화를 측정하기 위해 층별로 동박 잔존율이 다른 8층 PCB를 제작하여 층별 두께를 측정하였다. 제시한 두께실험식을 검증하기 위해 두께실험식으로 도출된 두께와 CCL 및 다층 PCB의 측정 두께를 비교하여 두께실험식의 신뢰성을 확인하였다.

2.1 CCL 제작 소재

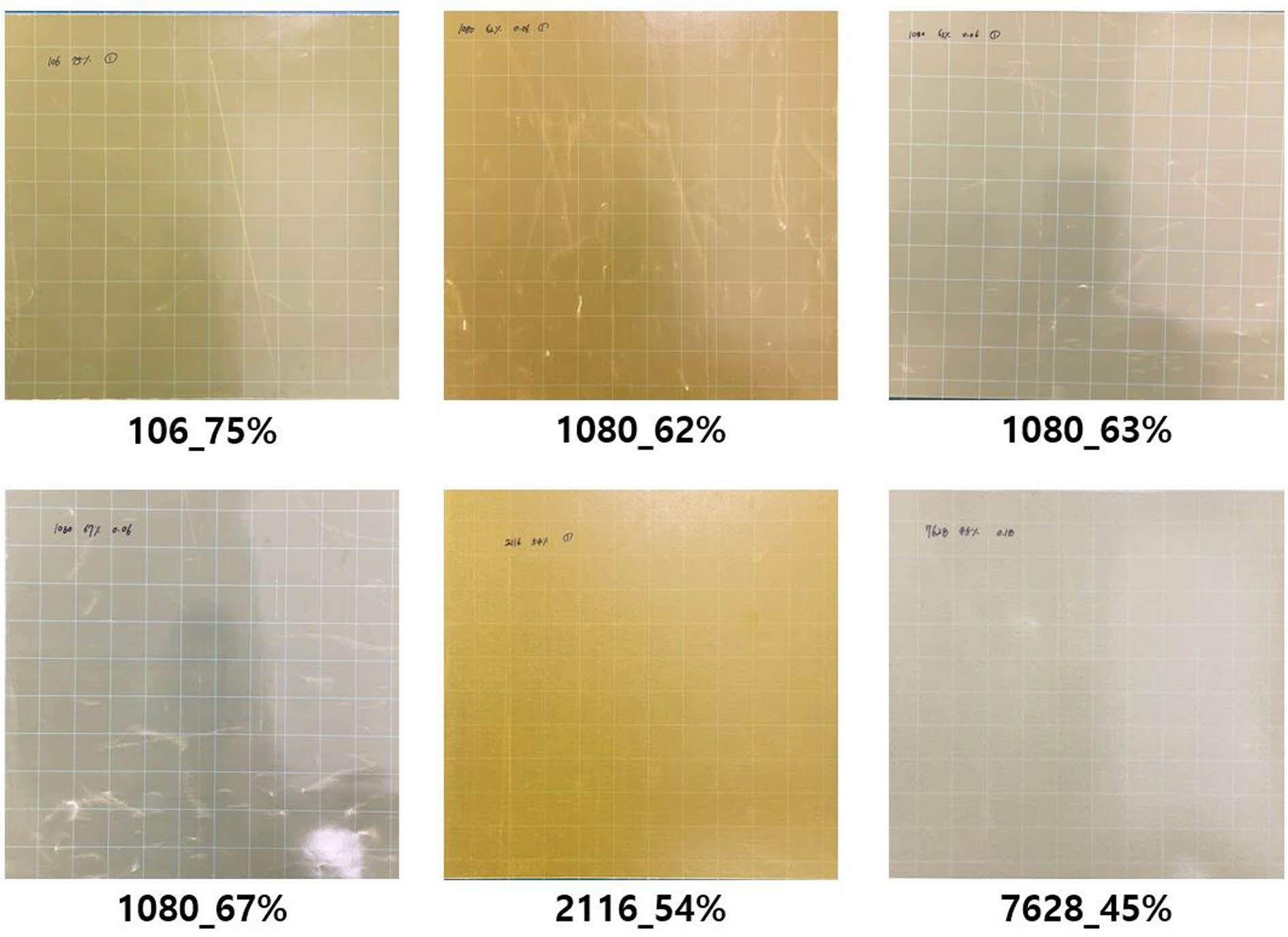

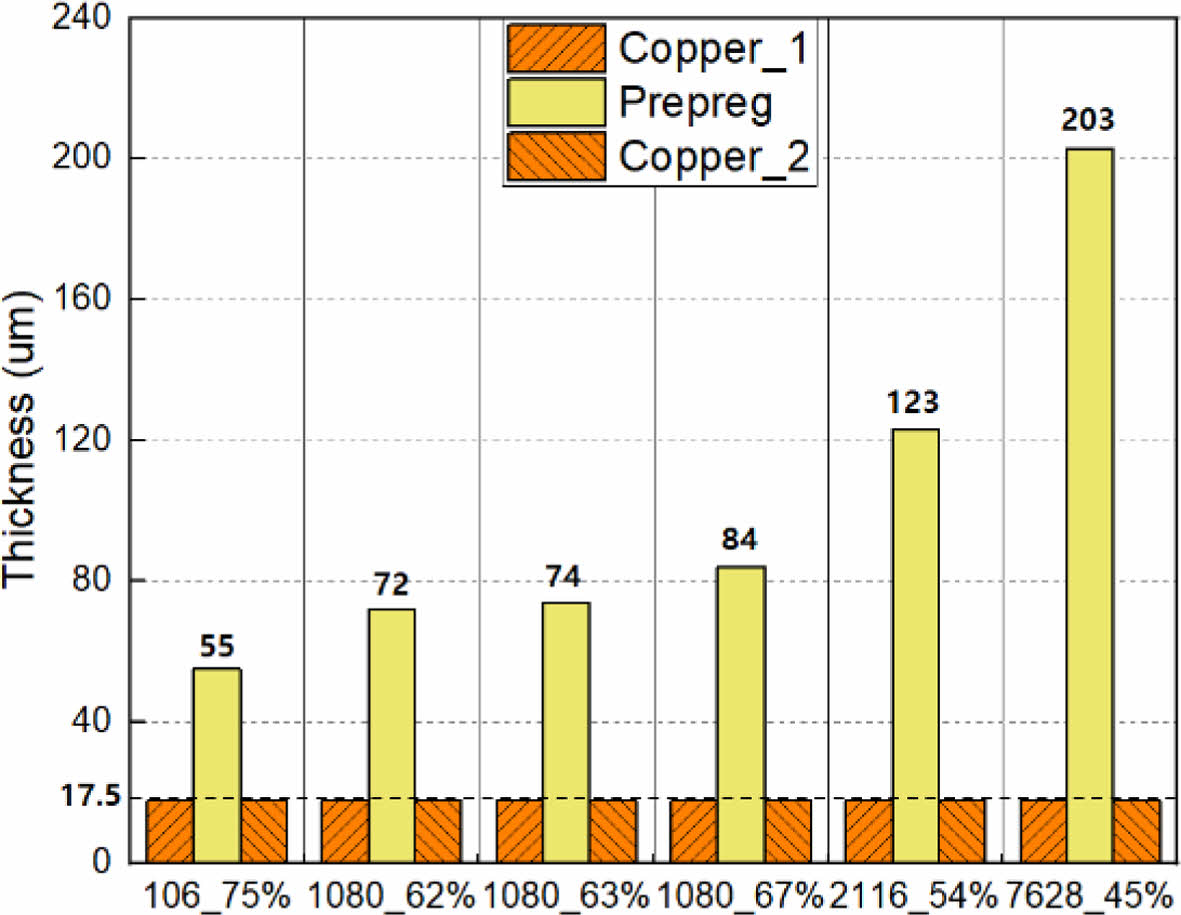

CCL 제작에는 6종류의 유리섬유/에폭시 프리프레그와 1/2 oz 동박이 사용되었으며, 사용된 프리프레그의 종류는 106_75%, 1080_62%, 1080_63%, 1080_67%, 2116_54% 7628_45%이다. 프리프레그 종류의 앞의 번호는 사용된 유리섬유 직물의 종류를 나타내며, 번호가 높을수록 더 촘촘하게 직조된 형태를 가진다. 또한 뒤의 번호는 무게를 기준으로 측정한 수지의 함유량을 나타낸다. Fig. 1은 연구에 사용된 유리섬유/에폭시 프리프레그 종류를 나타낸다.

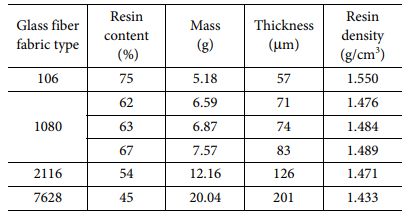

프리프레그의 물성을 파악하기 위해 마이크로미터와 전자저울을 사용하여 두께 및 질량 측정을 진행하였다. 프리프레그를 230 × 230 mm로 재단하여 질량을 측정하였고 두께는 총 8개의 지점을 선정하여 측정하였다. 프리프레그의 유리섬유의 밀도는 2.54 g/cm3로 같지만 수지의 경우 제조사가 사용하는 수지의 종류 및 프리프레그의 두께와 질량 측정시 발생하는 오차로 인해 수지의 밀도가 다를 수 있기 때문에 여러 종류의 프리프레그를 사용하여 각각 측정하였으며, 측정 결과를 활용하여 수지 밀도를 도출하였다. 그 결과 밀도가 평균적으로 1.484 g/cm3로 나타났으며, 최대 오차가 4.45%로 확인하였다. 두께 실험식에 적용되는 수지 밀도는 평균값을 사용하였다. Table 1은 본 연구에 사용된 프리프레그의 구성과 특성을 나타낸다.

2.2 CCL 제작 공정

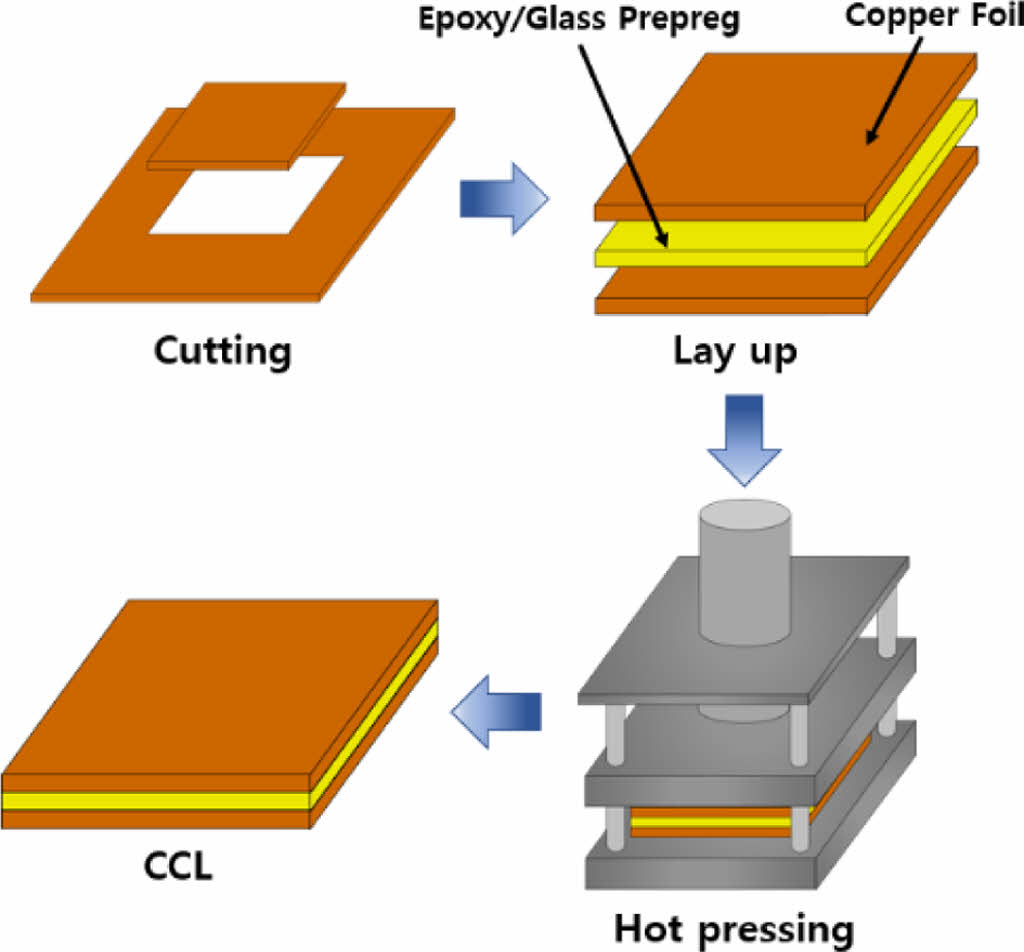

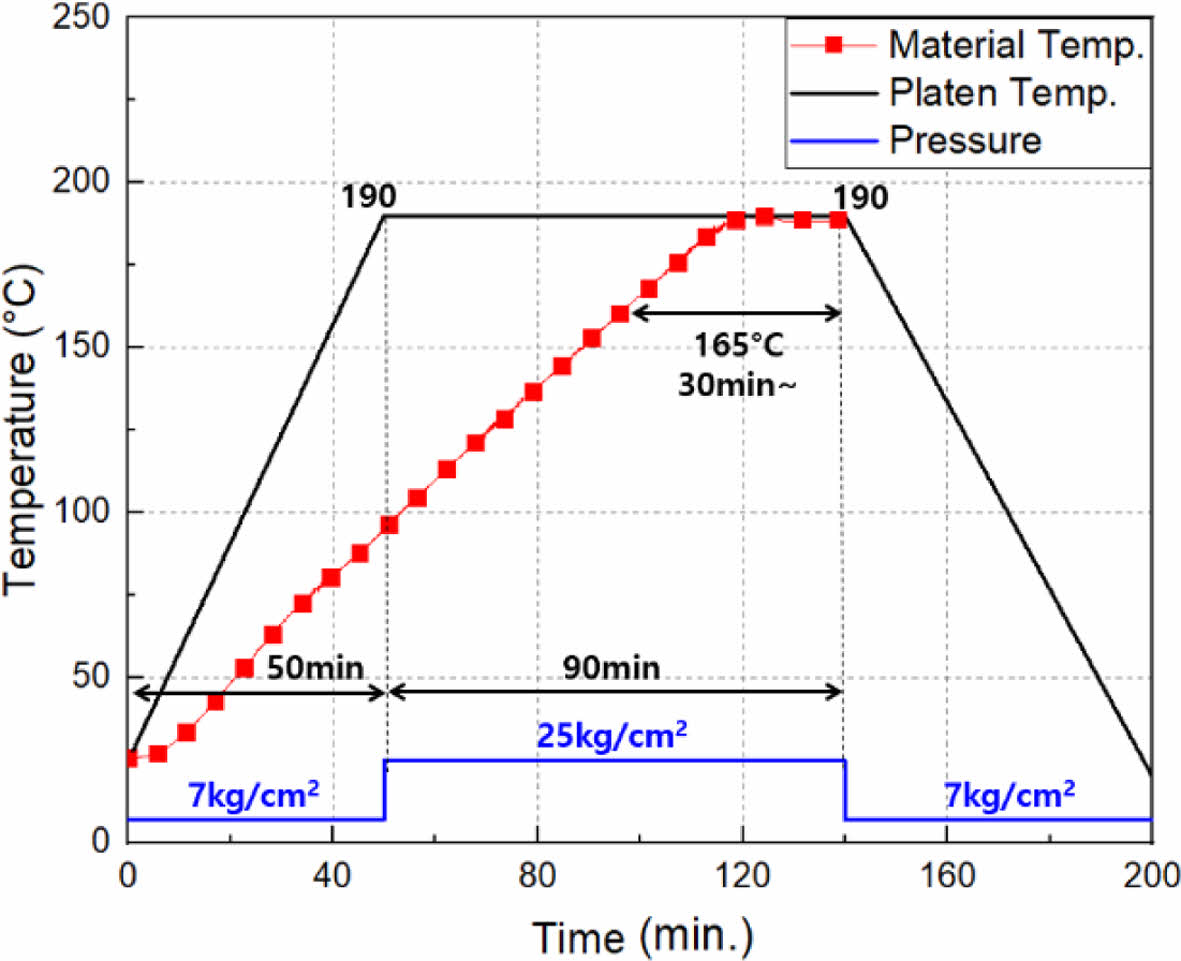

CCL은 Fig. 2와 같이 프리프레그와 동박을 적층하고 가열 및 가압을 통해서 제작되며, 본 연구에서는 핫 프레스기를 사용하여 가압 및 가열 공정을 수행하였다. 제작 온도 및 압력 조건은 Fig. 3과 같이 7 kg/cm2의 압력을 부여하고 상온에서 1.5oC/min의 속도로 소재온도가 승온하도록 설정하였다. 이후 소재 온도가 90~100oC에 서 압력을 25 kg/cm2으로 높이고 소재 온도가 165oC에 도달하면 30분 이상을 유지하여 제작하였다.

2.3 CCL 두께 측정

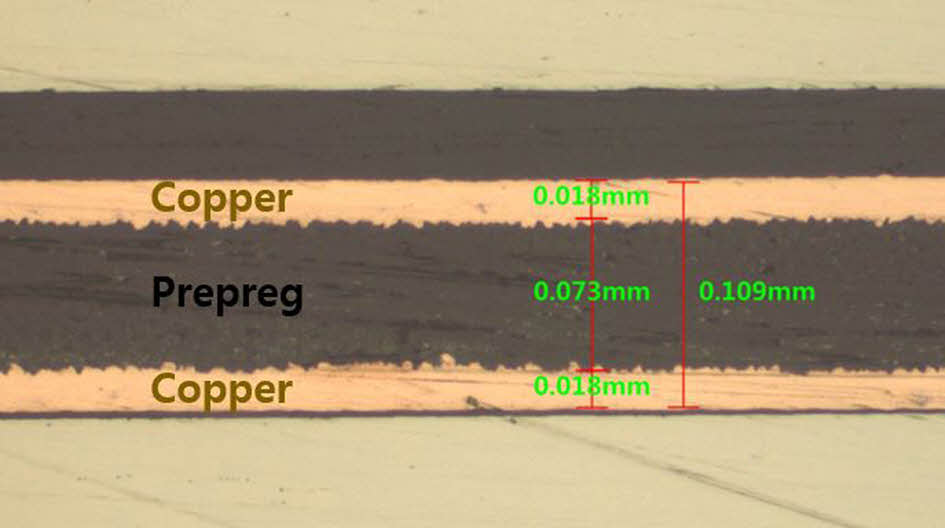

앞서 제작된 CCL의 건전성을 확인하기 위해 8개의 지점을 선정하여 두께를 측정한 결과를 비교하였고 두께 편차가 최대 3.05% 이내로 제작 공정이 잘 이루어진 것을 확인하였다. 층별 두께를 측정하기 위하여 CCL을 재단하여 샘플을 제작하였고 광학 현미경을 사용하여 측정을 진행했다. Fig. 4는 현미경으로 측정한 단면을 나타내며, Fig. 5는 제작한 CCL 층별 두께에 대한 그래프를 나타낸다.

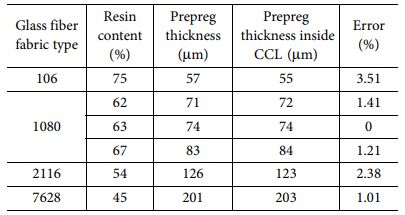

광학 현미경을 통해 CCL의 각 층에 따른 단면 두께를 측정한 결과 동박의 두께는 17~18 mm로 일정한 것을 확인하였고 프리프레그의 두께는 Table 2와 같이 CCL 제작 전과 후의 두께 차이가 미비하거나 없는 것을 확인하였다. 이는 동박 잔존율이 100%이기 때문에 CCL 제작 후 프리프레그의 두께 변화가 없는 것을 알 수 있다.

|

Fig. 1 Glass/Epoxy prepreg |

|

Fig. 2 Manufacturing processes for copper clad laminate |

|

Fig. 3 Curing cycles of copper clad laminate |

|

Fig. 4 Cross section of copper clad laminate |

|

Fig. 5 Layer thicknesses of the manufactured CCL |

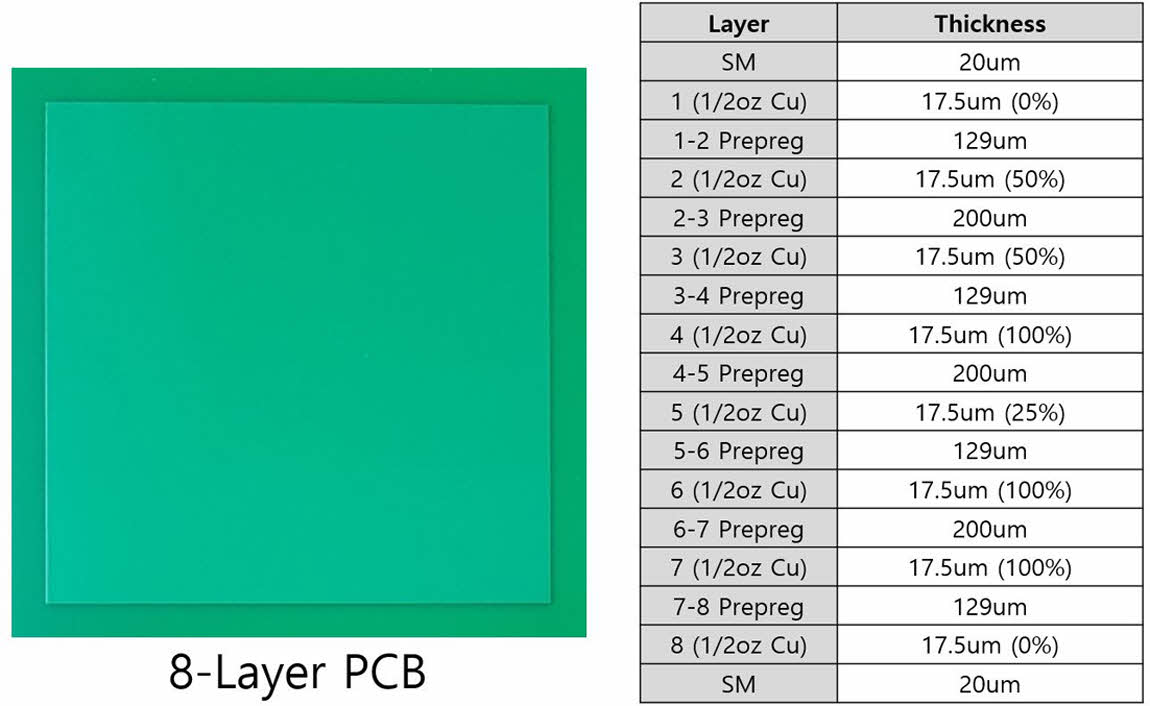

동박 잔존율에 따른 프리프레그의 두께 변화를 측정하기 위해 동박 잔존율을 0%, 25%, 50%, 100%로 각 층별로 차이를 주어 8층 PCB를 제작하였다. Fig. 6은 8층 PCB의 구성 및 동박 잔존율을 나타낸다.

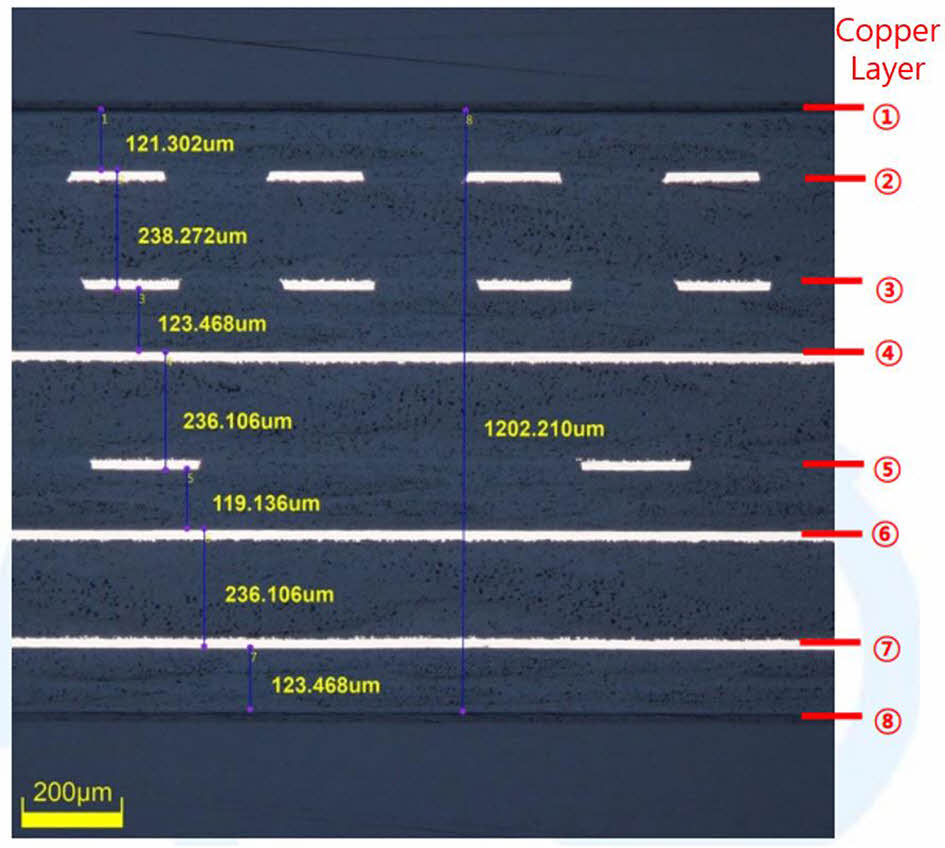

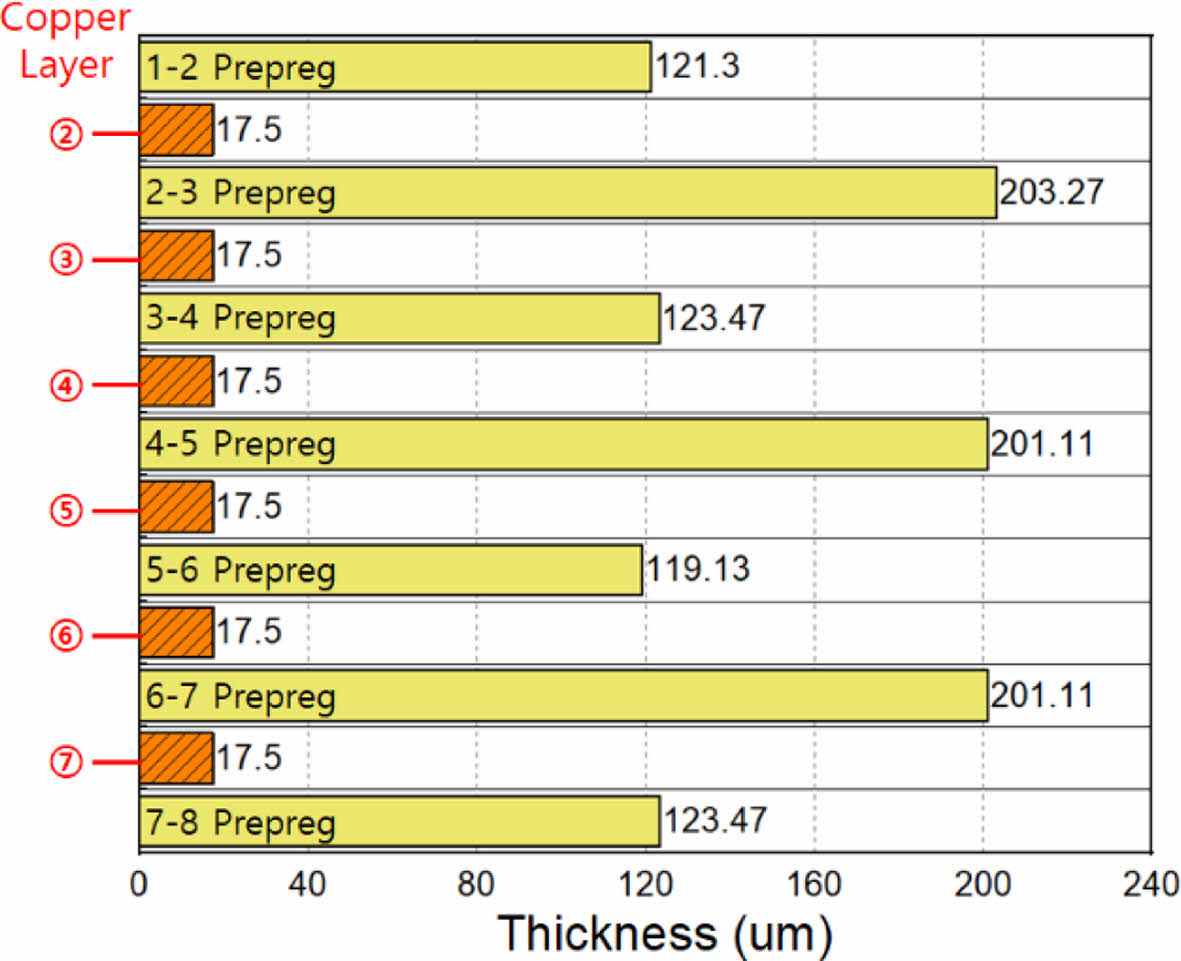

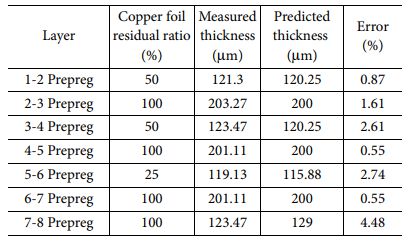

다층 PCB의 층별 두께를 측정하기위해 현미경을 사용하여 단면을 촬영하였다. 두께 측정 결과, 이미 경화가 되어 고체 상태인 Core 부분은 두께가 변화하지 않기 때문에 2-3, 4-5, 6-7 프리프레그를 제외한 나머지 프리프레그의 두께가 119.13~123.47 μm를 확인하였고 기존에 설계된 129 mm보다 감소된 것을 확인하였다. 또한 동박 잔존율이 낮을수록 프리프레그의 두께가 더 많이 감소되는 것을 확인하였다. Fig. 7은 8층 PCB의 단면을 나타내며, Fig. 8은 8층 PCB 층별 두께에 대한 그래프를 나타낸다.

|

Fig. 6 Layer structure for 8-layerd PCB |

|

Fig. 7 Cross section of 8-layerd PCB |

|

Fig. 8 Measured layer thicknesses of 8-layerd PCB |

4.1 두께 실험식 제시

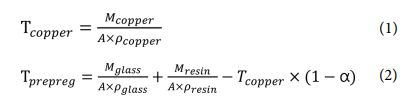

측정된 소재의 물성을 사용하여 설계된 CCL과 다층 PCB의 두께를 예측하기 위해 각 층별 구성 소재에 대한 두께 실험식을 식 (1), 식 (2)와 같이 제시하였다. 식 (1)에는 동박의 질량, 면적 및 밀도에 대한 동박의 두께 실험식을 나타내며, 식 (2)에 유리섬유 및 수지의 밀도, 면적 및 질량 그리고 동박 잔존율에 따른 두께 감소를 고려한 프리프레그의 두께 실험식을 나타낸다. 이때 사용되는 동박의 두께는 CCL과 프리프레그의 사이에 적층되는 동박의 두께를 나타낸다. T는 두께, A는 면적, M은 질량, ρ는 밀도, α는 동박 잔존율을 나타낸다.

4.2 두께 실험식 검증

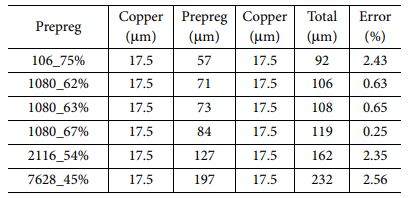

제시한 두께 실험식을 검증하기위해 제작한 CCL의 두께 측정값과 실험식을 통한 두께 예측값을 비교하였다. 두께 실험식에 사용된 수지 밀도는 6종류 프리프레그의 수지 밀도에 평균값인 1.484 g/cm3으로 계산하였다. 측정값과 예측값 사이의 최대 오차는 2.56%이며, 7628_45% 프리프레그를 사용하여 제작한 CCL에서 발생함을 확인하였다. 이를 통해 CCL의 경우 동박 잔존율이 100%이기 때문에 프리프레그의 두께 변화가 없어 실험식을 통한 두께 예측값과 잘 일치하는 것 확인할 수 있다. Table 3은 두께 실험식을 활용한 CCL의 두께 예측값을 나타낸다.

두께 실험식에서 동박 잔존율에 따른 프리프레그의 두께 변화를 적용하였고 이를 확인하기 위해 현미경으로 측정한 8층 PCB의 층별 두께와 실험식을 통해 계산된 두께를 비교하였다. 측정값과 실험식을 통한 두께 예측값의 최대 오차는 4.48%로 확인하였으며, 실험식과 잘 일치하는 것을 확인하였다. 측정된 8층 PCB의 전체 두께는 설계된 두께보다 약 20 mm 감소하였으며, 실험식을 토대로 계산된 8층 PCB의 두께와는 약 11 mm 차이나는 것을 확인할 수 있다. Table 4는 8층 두께 실험식을 통한 두께 예측값을 나타낸다.

본 연구에서는 다층 PCB의 정확한 두께 설계를 위해 두께 실험식을 제시하였고 다층 PCB에 사용되는 유리섬유/에폭시 프리프레그의 밀도와 동박 잔존율을 파악하여 두께를 예측하는 연구를 수행하였다. 다층 PCB에 사용되는 소재의 물성을 파악하기위해 유리섬유/에폭시 프리프레그의 질량과 두께를 측정하였고 측정된 소재를 사용하여 CCL을 제작하였다. 또한 동박 잔존율에 따른 두께 변화를 확인하기 위해 다층 PCB를 설계 및 제작하였고 두께를 측정하였으며, 측정된 결과와 두께실험식을 통해 예측된 결과를 비교하여 두께실험식을 검증하였다.

(1) CCL의 두께 설계를 진행하기 위해 총 6종류의 유리섬유/에폭시 프리프레그의 밀도, 질량 그리고 두께를 측정하였으며, 측정된 소재를 활용하여 CCL을 제작하였다. 제작된 CCL의 건전성을 확인하기 위해 총 8개의 지점을 선택하여 두께를 측정하였고 편차가 3.05%의 이내로 제작 공정이 잘 이루어진 것을 확인하였다. 층별 두께 측정결과 기존 프리프레그의 두께와 공정 후 두께의 변화가 없는 것을 확인하였다.

(2) 동박 잔존율에 따른 프리프레그의 두께 변화를 확인하기 위해 0%, 25%, 50%, 100%로 동박 잔존율을 구성하여 8층 PCB를 설계 및 제작하였고 현미경을 사용해 층별 두께를 측정하였다. 측정 결과 Core 부분을 제외한 프리프레그의 두께가 119.13~123.47 μm로 측정되었고 기존 설계한 129 mm 두께 보다 최대 약 10 μm 감소한 것을 확인하였다. 또한 동박 잔존율이 낮을수록 두께 감소가 더 큰 것을 확인하였다.

(3) 두께 실험식 검증을 위해 CCL과 8층 PCB의 단면 두께 측정 결과와 예측된 두께 결과를 비교하였다. CCL의 경우 최대 2.56%의 오차를 가지며 동박 잔존율이 100%이기 때문에 두께 실험식과 잘 일치하는 것을 확인할 수 있었다. 8층 PCB의 경우 최대 4.48%의 오차를 확인하였으며, 이것은 하나의 프리프레그 층에 대한 오차이고 산업용 다층 PCB의 경우 전체 두께 오차가 5~10% 이내이기 때문에 잘 예측되었다고 판단된다.

(4) 8층 PCB의 전체 두께는 기존에 설계했던 두께보다 약 20 mm 감소하였고 이는 전체 두께로 보았을 때 미비할 수 있지만 8층이 아닌 더 많은 층으로 구성되고 더 적은 회로밀도로 구성된 다층 PCB의 경우 두께 변화가 더 크게 일어날 수 있기 때문에 두께 실험식을 통해 두께가 감소되는 것을 고려하여 설계하는 과정이 필요하며, 두께 실험식으로 예측된 두께를 기준으로 정확한 기판의 내구성 및 성능을 파악할 수 있을 것으로 판단된다.

- 1. Cho, S.H., Jung, H.I., and Bae, O.C., “Numerical Analysis on the Design Variables and Thickness Deviation Effects on Warpage of Substrate for FCCSP,” Journal of the Microelectronics & Packaging Society, Vol. 19, No. 3, 2012, pp. 57-62.

-

- 2. Kim, C.G., and Lee, S.S., “Ultra-High-Speed PCB Design Methods,” Institute of Korean Electrical and Electronics Engineers, Vol. 22, No. 3, 2018, pp. 882-885.

-

- 3. Oh, S.H., Kim, J.G., Park, K.H., Im, C.W., and Kang, K.I., “A PCB Material Selection, Test and EMI Simulation for 10Gbps High Speed IO Data Processing Board,” KSAS 2010 Conference, 2010, pp. 903-906.

- 4. Cho, S.H., Jang, J.Y., Kim, J.C., Kang, S.W., Sung, I., and Bae, K.Y., “A Study on Heat Transfer Characteristics of PCBs with a Carbon CCL,” Journal of the Microelectronics and Packaging Society, Vol. 22, No. 4, 2015, pp. 37-46.

-

- 5. Jiru, M., Guozheng, L., and Lei, Z., “Study on Epoxy Matrix Modified with Poly(2,6-dimethyl-1,4-phenylene ether) for Application to Copper Clad Laminate,” Composites Science and Technology, Vol. 62, No. 6, 2002, pp. 783-789.

-

- 6. Kim, S.M., Ku, T.W., Song, W.J., and Kang, B.S., “Experimental Study on the Improvement of Flexural Strength in Slim Multi-Layer Printed Circuit Boards,” Proceedings of the KSME Conference, 2007, pp. 321-325.

- 7. Yoon, I.S., “Warpage Improvement of PCB with Material Properties Variation of Core,” Journal of the Microelectronics & Packaging Society, Vol. 13, No. 2, 2006, pp. 1-7.

- 8. Kim, C.G., and Lee, S.S., “Ultra-High-Speed PCB Design Methods”, Journal of IKEEE, Vol. 22, No. 3, 2018, pp. 882-885.

-

- 9. Lee, S.H., and Kim, S.K., “Optimal Design of Dummy Patterns for Minimizing PCB Warpage,” Transactions of the KSME, A, Vol. 33, No. 6, 2009, pp. 577-583.

-

- 10. Yoon, D.H., Cho, M.G., and Lin, C.H., “Implementation of Multi-layer PCB Design Simulator for Controlled Impedance,” Journal of the Institute of Electronics and Information Engineers, Vol. 48, No. 12, 2011, pp. 73-81.

This Article

This Article

-

2022; 35(3): 182-187

Published on Jun 30, 2022

- 10.7234/composres.2022.35.3.182

- Received on Mar 13, 2022

- Revised on Apr 25, 2022

- Accepted on May 10, 2022

Services

Services

Shared

Correspondence to

Correspondence to

- Kwang-Bok Shin

-

Department of Mechanical Engineering, Hanbat National University

- E-mail: shin955@hanbat.ac.kr

Copyright ⓒ The Korean Society for Composite Materials. All rights reserved.

Copyright ⓒ The Korean Society for Composite Materials. All rights reserved.