- Prediction of the Warpage for Large-scale Semiconductor Package Using Equivalent Model Considering the Anisotropic Thermomechanical Properties Based on Multi-physics Simulation

Woong-Kyoo Yoo*, Jeong-Hyeon Baek*, Jong-Whi Park*, Hak-Sung Kim*,**†

* Department of Mechanical Convergence Engineering, Hanyang University, Seoul, Republic of Korea

** Hanyang Research Center for Advanced Semiconductor Packaging, Hanyang University- 다중 물리 시뮬레이션 기반 이방성 열-기계적 특성을 고려한 등가 모델링 활용 대면적 반도체 패키지의 워피지 예측

유웅규* · 백정현* · 박종휘* · 김학성*,**†

This article is an open access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/4.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

With the rise of new industrial paradigms such as AI and autonomous driving, semiconductors have become essential components across various platforms, from data centers to personal devices. As demands for high performance, high integration and lightweight packaging grow, challenges such as warpage arise due to large-area structures and heterogeneous materials. Although simulation-based warpage prediction methods have been developed, fully reflecting high-resolution circuit patterns in finite element model leads to excessive mesh counts, increasing computational cost and reducing numerical stability. To overcome these issues, in this research, proposal of the modeling approach that specifies Cu pattern orientation and density in each region of high-resolution circuit images. These analyzed results are used to construct an equivalent model with effective anisotropic thermo-mechanical properties. This method enables efficient thermo-mechanical analysis while preserving key circuit characteristics, allowing accurate warpage prediction in semiconductor packages.

인공지능, 자율주행 등 새로운 산업 패러다임의 부상 속에서 반도체는 핵심 부품으로 자리매김하고 있다. 반도체는 대규모 데이터를 처리하는 데이터 센터는 물론, 개인용 통신기기에 이르기까지 다양한 플랫폼에 적용되며, 이에 따라 반도체 패키지의 고성능화, 고집적화, 경량화에 대한 요구가 빠르게 증가하고 있다. 그러나 대면적 구조와 이종 소재의 사용은 작동 중 발열과 함께 워피지(warpage)와 같은 신뢰성 문제를 유발한다. 이러한 문제를 해결하기 위해 다양한 시뮬레이션 기반 워피지 예측 기법이 제안되고 있으나, 실제 회로 패턴을 고해상도로 모두 반영할 경우 유한요소해석(FEA)에 필요한 메쉬 수가 기하급수적으로 증가하여 계산 비용이 크게 늘어나고, 수치적 안정성도 저하되는 한계가 있다. 본 연구에서는 이러한 한계를 극복하고자, 고해상도 회로 이미지를 일정 구획으로 분할하고, 각 구획별 배선의 방향성과 밀도를 정량화하여 등가화된 해석 모델을 구축하였다. 이를 유한요소 해석에 적용함으로써, 회로 형상의 실제 특성을 유지하면서도 계산 효율을 확보한 열-기계 연성 해석이 가능함을 확인하였다. 또한, 각 구획의 특성을 반영한 유효 이방성 열-기계적 물성을 도출하여 반도체 패키지 휨을 예측하였다.

Keywords: 반도체 패키지(Semiconductor package), 신뢰성 평가(Reliability evaluation), 휨(Warpage), 등가모델(Equivalent model), 다중 물리 연성 해석(Multi-physics simulation)

반도체는 최근 인공지능을 활용한 새로운 국면의 산업에서 중요한 구성요소이다. 크게는 수많은 데이터를 저장하는 데이터 센터부터 작게는 사용자의 개인 통신기기에까지 다양한 형태로 내장되어 있다. 이를 만족하기 위해 최근 데이터 센터와 차량용 고성능 시스템에 적용되는 반도체 패키지는 고속 연산, 저전력 특성을 동시에 만족시키기 위해 초박형, 초경량화되고 있으며, 동시에 패키지 내에는 다수의 칩과 회로 소자들이 고집적화되고 있다[1]. 이러한 대면적 고집적 패키지는 열 발생량이 크고, 회로 배선 구조가 복잡하며, 다양한 재료들이 복합적으로 구성되어 있어 신뢰성 확보가 더욱 어려워지고 있다. 실제로 패키지 설계 단계에서부터 공냉, 수냉, 침지 냉각 등 다양한 냉각 조건이 적용되지만, 패키지 내 소재 간 기계적 물성 차이로 인한 열-기계적 불균일성으로 인해 워피지(warpage)가 발생하고, 이는 전기적 연결 불량, 소자 손상, 시스템 전체의 성능 저하 등 치명적인 신뢰성 문제를 유발할 수 있다[2]. 2024년 유럽 자동차 제조사는 이종접합 패키지의 열변형으로 인해 ADAS 센서 오작동이 발생하며 12만 대 차량을 리콜한 사례가 있다. 리콜 된 차량 중 이는 전체 결함의 34%가 차량용 반도체 패키지의 작동 중 기계적 물성 차이로 인한 워피지로 인해 계면 결함에서 기인한 것으로 확인되었다. 또한 비슷한 예로, Google 클라우드 장애 보고서(2025)에 따르면, 고밀도 GPU 패키지의 열변형이 서버 다운타임의 22% 원인으로, 시간당 270만 달러의 손실을 발생시킨 사례가 있다[3,4].

이러한 워피지 문제의 심각성과 중요성으로 인해, JEDEC과 같은 국제 공인 기관에서는 반도체 패키지의 신뢰성 평가를 위한 기준들을 제시하고 있다[5]. 이를 만족하기 위한 다양한 소재 조합 및 패키지 구조에 대한 연구가 활발히 진행되고 있으며, 실제 제품 적용을 위해 이러한 기준을 충족하는 설계를 수행하려면 작동 중 발생하는 워피지를 정밀하게 예측할 수 있는 시뮬레이션 기반 해석 기법이 필수적이다.

특히, 반도체 소자 작동 중에는 회로의 전류 흐름에 따라 도선 저항에 의한 열(Joule heating)이 발생하고, 이 열이 패키지 내부에 비등방적으로 분포된다. 불균일한 배선 밀도에 따라 분포된 열은 온도에 의존적인 기계적 물성 차이에 의해 복잡한 응력 및 변형을 유발한다. 따라서, 작동 중 발생한 열을 쉽게 배출하는 연구뿐만 아닌 이러한 기계적 신뢰성을 향상 시킬 수 있는 단순한 기계적 물성만이 아닌, 열 물성까지 향상된 소재의 개발이 성행중이다. 하지만, 개발된 소재를 적재적소에 활용하거나, 다양한 패키지 구조를 확인하기 위해 워피지를 예측하기 위한 다양한 시뮬레이션 기술들이 개발되고 있다.

하지만 다양한 설계 변수들의 영향을 정확하게 파악하기 위해 실제 회로 패턴의 미세한 형상과 다층 구조를 모두 패석 모델에 직접 반영하려 할 경우, 현실적인 제약이 발생한다. 복잡한 배선과 층간 구조를 고해상도로 구현하면 유한요소해석(FEA)에 필요한 메쉬 수가 폭발적으로 증가하게 되며, 그에 따라 계산 시간과 메모리 요구량도 급증한다. 특히 작동 중 열-기계 연성 문제를 포함한 비선형 해석에서는 각 시간 스텝마다 연산량이 누적되기 때문에, 수치적 안정성과 계산 자원의 효율성 측면에서 매우 비경제적이다. 이로 인해 실제 산업 현장에서는 시뮬레이션의 정밀도와 계산 효율성 사이에서 최적의 균형을 찾는 것이 핵심 과제로 떠오르고 있으며, 복잡도를 줄이면서도 물리적 특성을 유지할 수 있는 등가화 기법의 도입이 필수적으로 요구되고 있다.

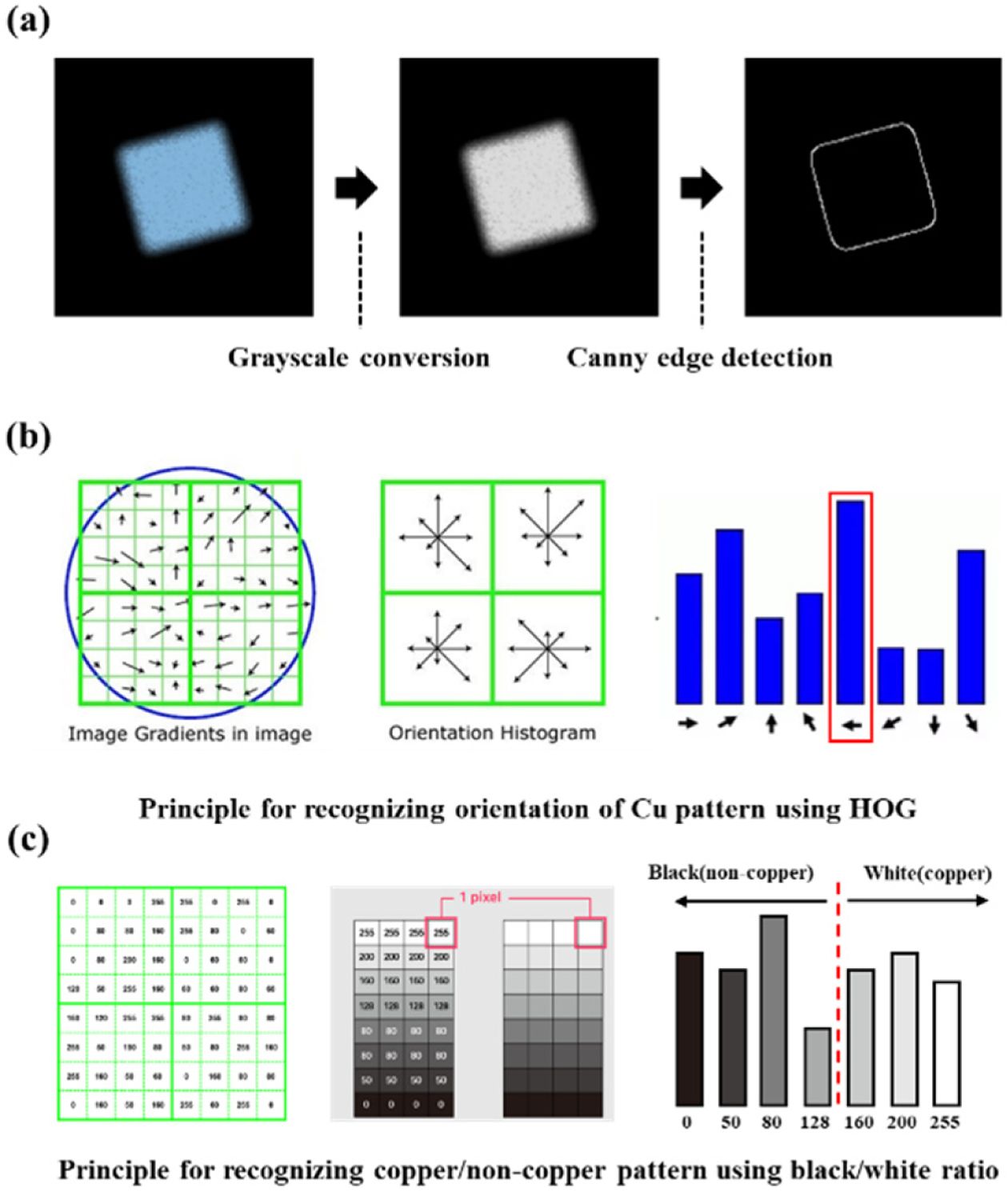

따라서, 본 연구에서는 이러한 한계를 극복하고자, 실제 회로 형상의 복잡도를 일정 수준으로 유지하면서도 구조적 특성을 충분히 반영할 수 있도록 회로 패턴을 일정 구획 단위로 구분하고, 각 구획 내의 배선 방향성과 밀도 정보를 기반으로 등가화된 패턴 모델을 구성하였다. 이 등가 패턴 분석을 위해 캐니 가장자리 검출 기법을 사용하여 배선 경계를 정밀하게 추출하고, 방향 벡터 분석 기법(HOG)을 통해 각 구획의 주요 배선 방향성을 정량적으로 분석하였다. 또한, 배선 밀도 분석을 통해 각 구획에서의 배선 밀도를 계산하였다.

회로를 등가화하기 위한 여러 분석 결과를 바탕으로 각 구획별 유효한 이방성 점탄성 물성과 이방성 열물성을 산정하였으며, 이를 통해 반도체 패키지의 작동 중 열의 구조와 회로의 방향성에 따라 분포되고, 결과적으로 워피지 거동 양상을 관찰하였다. 이 과정을 자동으로 분석하고 유한요소해석을 통해 수행함으로써, 회로 형태를 간접적으로 반영한 등가 패턴을 활용한 실효성 있는 열-기계적 연설 해석 결과를 확보하였다.

반도체 패키지를 구성하는 회로는 금속 패드 또는 논리적 구조를 갖는 배선과 같은 복잡한 형태로 구성되어 있다. 본 연구에서는 이를 등가화하기 위해 각 배선층의 이미지를 활용하여 분석하였다. 이러한 방법은 회로 설계 도구로부터 얻어지는 불필요한 데이터를 제외하고 분석한다는 장점이 있다. 분석 정확도를 향상시키기 위해 파이썬 (Python) 기반의 다양한 이미지 처리를 수행하였다.

2.1 전처리

회로 이미지 내에서 배선 경계를 정확하게 추출하는 전처리 과정이 선행되어야 하며, Fig. 1(a)에 나와 있는 캐니 가장자리 검출 기법은 이를 위한 효과적인 알고리즘이다. 이 방법은 가우시안 스무딩을 통한 노이즈 제거, 임계 요소 계산, 가장자리 세선화, 이진화 임계값 처리를 순차적으로 수행함으로써 고정밀 경계 추출이 가능하다[6]. 특히 경계선의 연속성, 방향성 보존, 노이즈 민감도 측면에서 우수한 성능을 보이며, 후속 단계인 HOG 기반 방향성 분석이나 배선 밀도 기반 밀도 계산의 정확도를 크게 향상시켰다.

2.2 방향성 분석

반도체 패키지 내 소자를 구성하는 배선들은 신호 및 전원 전달을 위해 복잡하게 라우팅(Routing)되어 있으며,다양한 각도로 위치되어 있다. 캐니 가장자리 검출 기법을 통해 경계가 추출된 후, 각 회로 구획의 배선 방향성을 정량화하기 위해 방향 벡터 분석 기법(HOG) 기법이 적용된다. 방향 성분 분석은 이미지 내 각 픽셀 주변의 방향 요소를 계산하고, 일정 블록 단위로 이 방향성을 히스토그램 형태로 누적하여 국소적인 패턴의 주된 방향을 파악한다[7]. 이 과정은 회로 배선이 일관된 방향성을 갖는 영역과 다방향으로 배선된 영역을 구분할 수 있게 하며, 각 구획의 대표 방향을 수치적으로 정의하였다.

2.3 배선 밀도 분석

회로 배선 밀도는 열적·기계적 물성에 큰 영향을 주는 인자로, 이를 정량화하기 위해 본 연구에서는 명도 기반 분석을 통해 배선의 부피 분율을 산출하였다. Fig. 1(c)에 나와 있듯 고해상도 이진화 이미지를 이용하여 각 구획 내 픽셀의 밝기 값을 기준으로 금속 배선과 절연체 영역을 구분하고, 전체 면적 대비 금속이 차지하는 비율을 계산하였다 . 이러한 명도 기반 분석은 단일 이미지에서 밀도 정보를 직관적으로 얻을 수 있다는 점에서 효율성과 실용성이 높아, 대면적 패키지의 물성 평가에 적합한 접근 방식으로 적용되었다.

이와 같은 방향성 및 배선 밀도 분석 결과는 각 구획에 손쉽게 적용할 수 있도록 행렬(Matrix) 형태로 저장되었으며, 이를 기반해 유한요소 해석에 필요한 물성 입력이 자동화되고, 통합적으로 관리될 수 있도록 하였다. 이러한 데이터 구조를 통해 분석 정확도와 작업 효율을 동시에 확보하였다.

2.4 패턴 분석 기법 적용 유한 요소 해석 모델

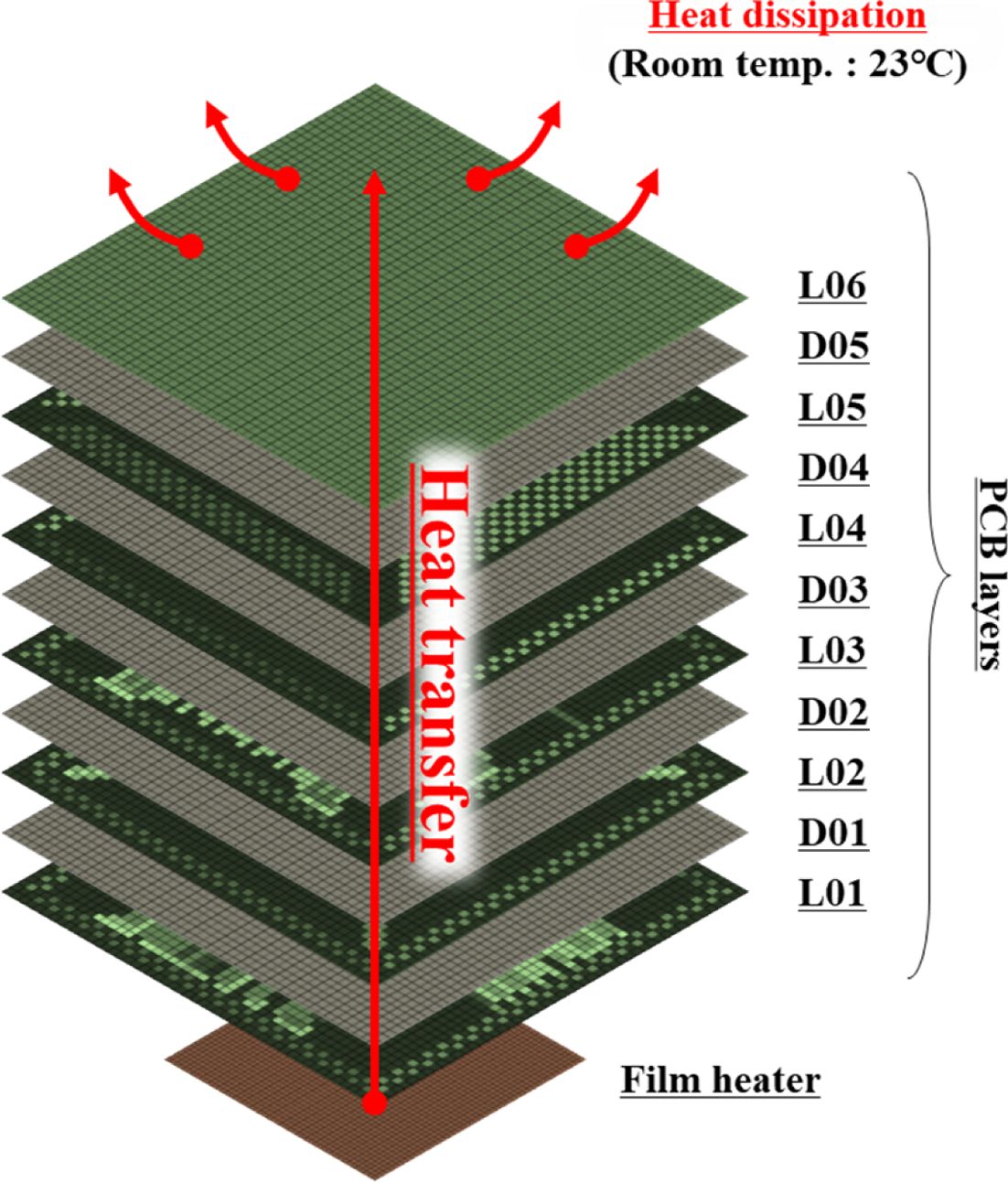

대면적 반도체 패키지에서 고집적 회로 구동 시 발생하는 온도 조건을 모사하기 위해, Fig. 2와 같이 대면적 PCB 기판 상에 열특성 평가용 패키지(Thermal Test Vehicle, TTV)를 모사한 박막 히터를 부착하였다. 히터는 내부 Joule heating을 통해 열원을 제공하며, 발생된 열은 접착층을 통해 하부 기판으로 전달된 후 PCB 전 영역으로 확산된다. 이 과정에서 패키지 내부의 다양한 재료 계면 및 기하학적 구조는 열 전달 거동에 영향을 미치며, 결과적으로 비균일한 열 분포와 워피지를 유발한다.

대면적 패키지는 고해상도 회로 패턴을 포함하고 있어 이를 직접적으로 모두 반영한 정밀 해석은 과도한 계산 자원을 요구한다. 따라서 본 연구에서는 회로 패턴 분석 결과를 기반으로 동일 구획 단위의 등가 모델을 구성하였다. 각 구획은 배선의 방향성과 밀도를 정량화한 행렬 정보를 바탕으로 이방성 점탄성 물성 및 열 물성을 부여받았으며, 이를 전체 패키지 유한요소 모델의 등가 입력값으로 적용하였다. 이를 통해 계산 효율성을 확보하면서도 패턴 인자 기반 이방성 거동을 반영할 수 있도록 하였다.

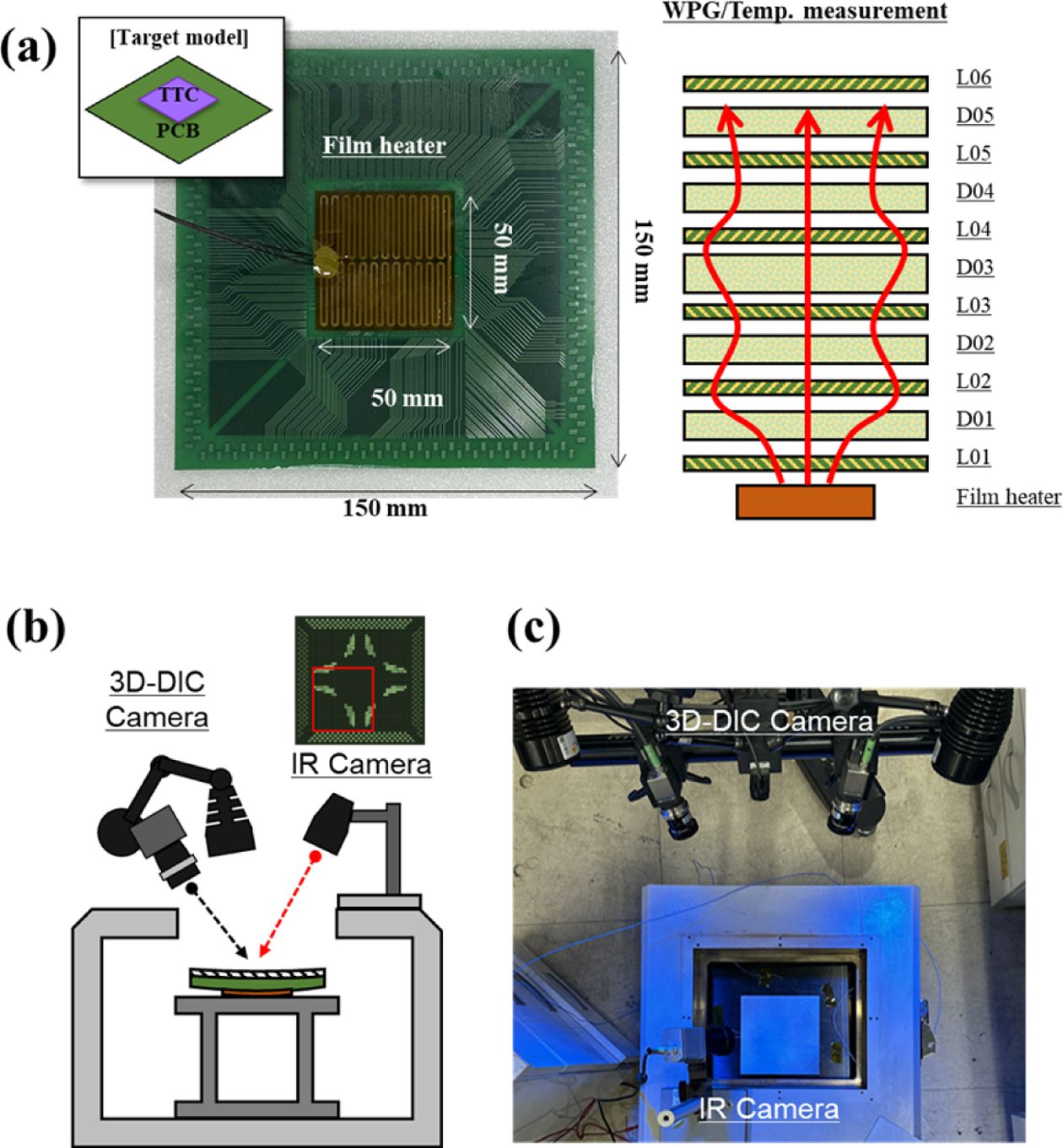

2.5 유한 요소 해석 기법 검증 실험

제안된 패턴 기반 등가 유한요소 해석 기법의 타당성을 검증하기 위해, Fig. 3과 같이 대면적 PCB 기판 상에 박막 히터를 부착하고 열-기계적 거동을 실험적으로 평가하였다. 히터에 전류를 인가하여 국부 열을 발생시켰으며, 생성된 열은 기판으로 전달된 후 PCB 전 영역으로 확산된다. 이 과정에서 발생하는 온도 분포 및 워피지 거동을 동시에 계측하였다.

온도 분포 측정을 위해 적외선(IR) 카메라를 사용하여 기판 표면의 실시간 열 분포를 비접촉 방식으로 관찰하였다. 이를 통해 열원의 위치와 시간에 따른 온도 확산 거동을 정량적으로 확보하였다.

동시에, 기판의 전면 변형 거동을 측정하기 위해 3D-디지털 이미지 상관 기법(3D-DIC) 시스템을 활용하였다. 시편 표면에 무작위 스페클 패턴을 형성한 후, 두 대의 카메라를 이용해 변형 전·후 이미지를 촬영하고 전장(full-field) 변위 및 변형률 분포를 계산하였다. 이를 통해 열 인가에 따른 실시간 워피지 변형을 정밀하게 계측하였다. 이를 통해 제안된 패턴 기반 등가 모델의 열-기계 연성 거동 예측 정확성을 검증하였다.

|

Fig. 1 Principle of image processing technique for equivalent pattern; a) Canny edge detection, b) Histogram of oriented gradients and c) Volume fraction analysis |

|

Fig. 2 (a) Experimental set-up and (b) Finite element model for validation and predicting heat transfer and warpage |

|

Fig. 3 (a) Experimental set-up and (b) Finite element model for validation and predicting heat transfer and warpage |

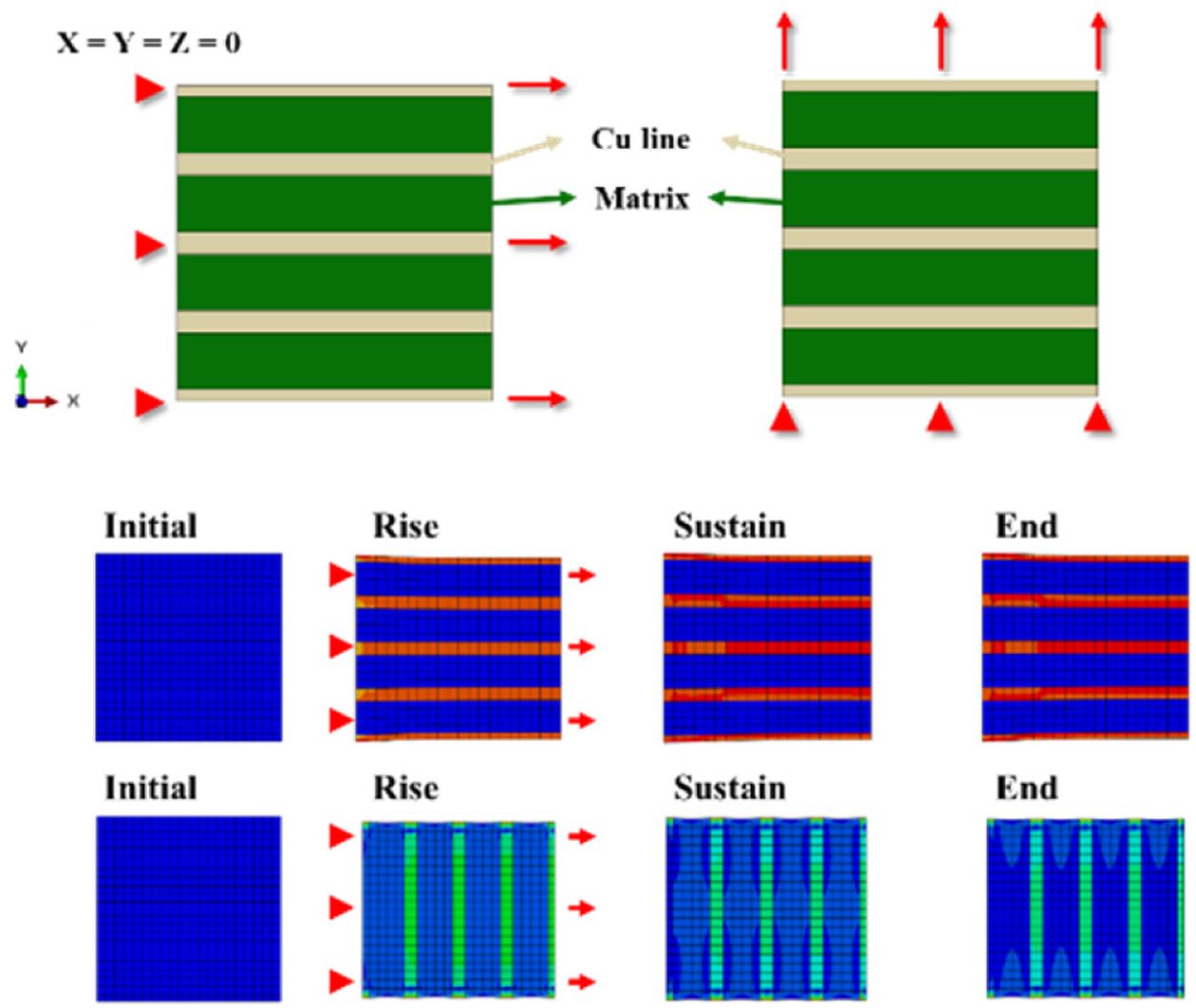

3.1 유효 기계적 물성

금속 배선의 배치 방향에 따른 이방성과, 폴리머 기반 절연체의 점탄성 특성이 결합된 이방성 점탄성 물성을 정의하였다. 선형 물성 적용이 가능한 구리 배선과 비선형 점탄성 물성의 적용이 요구되는 폴리머 기반 절연체로 구성된 패턴들은 방향에 따라 기계적 물성이 달라지며, 시간 및 온도에 의존적인 점탄성 특성을 가지며 이를 이방성 점탄성이라 일컫는다[8]. 이를 반영하기 위해 Fig. 4에서 처럼 각 패턴 단위에 대해 유한요소해석(FE)을 수행하였다.

시뮬레이션 결과를 기반으로 프로니 계수를 활용해 선형 응력 완화 탄성계수가 계산되었다. 시간과 온도는 WLF (Williams-Landel-Ferry) 모델을 이용해 보정되었으며, 복합재료 적층 이론에 기반하여 복합재료 적층 이론 기반 (ABD) 행렬을 도출하였다. ABD 행렬은 Table 1의 점탄성 물성 계수를 반영하여 시간/온도 의존적으로 계산되었다. 동일한 방식으로 구리 및 FR4의 온도 의존적 열팽창계수 또한 도출되었다. 최종적으로, 이방성 점탄성 물성과 열팽창 특성은 유한요소 해석 내 서브루틴에 적용되어, 효과적이고 정밀한 워피지 예측 해석을 수행하였다.

3.2 유효 열적 물성

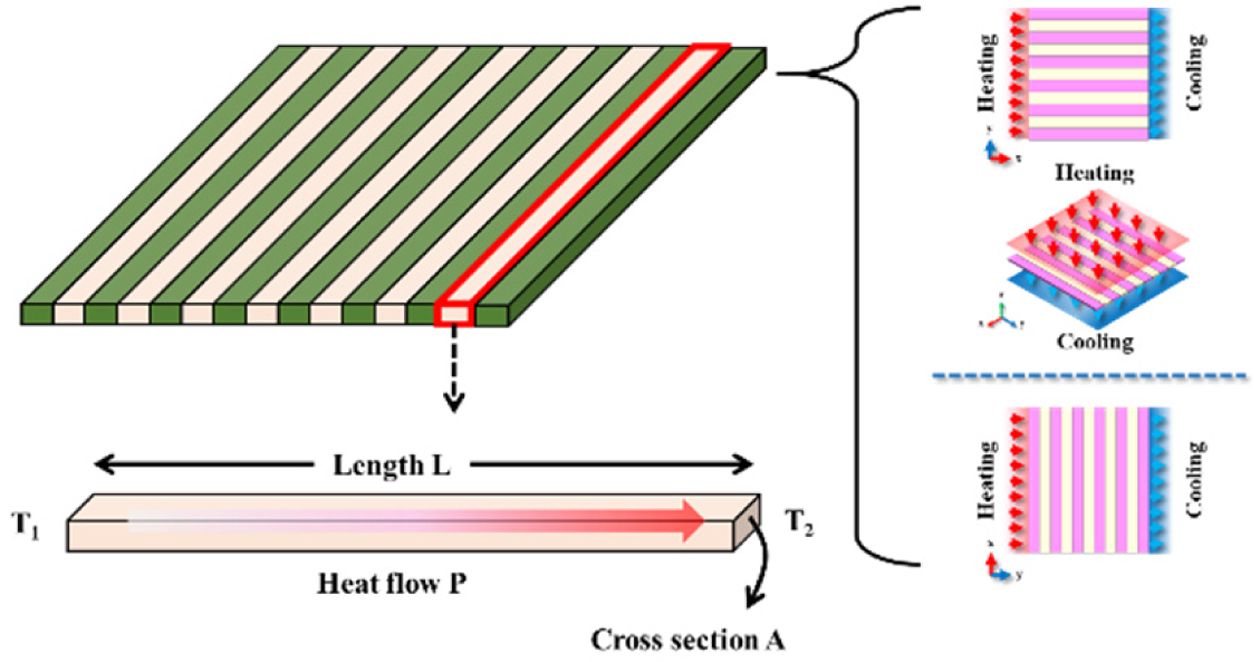

회로 패턴의 방향성과 배선 밀도는 열 전달 경로에 직접적인 영향을 미치기 때문에, 이를 기반으로 한 유효 열전도도 도출은 패키지의 열-기계 해석에서 매우 중요한 요소이다. 앞서 정량화된 배선 방향성과 부피 분율을 고려한 평면 패턴 모델을 활용하여 유효 열전도도를 도출하였다. Fig. 5 에서 보여지듯 선형 배열된 구리 배선과 절연체가 주기적으로 반복되는 복합 구조를 가정하고, 직렬/병렬 열 저항 개념을 적용하여 x축(배선 방향)과 y축(배선 수직 방향)에 따른 유효 열 저항을 각각 계산하였다.

|

Fig. 4 Finite element model for anisotropic viscoelastic properties |

|

Fig. 5 Thermal calculation model for effective anisotropic properties |

4.1 물성 도출 결과

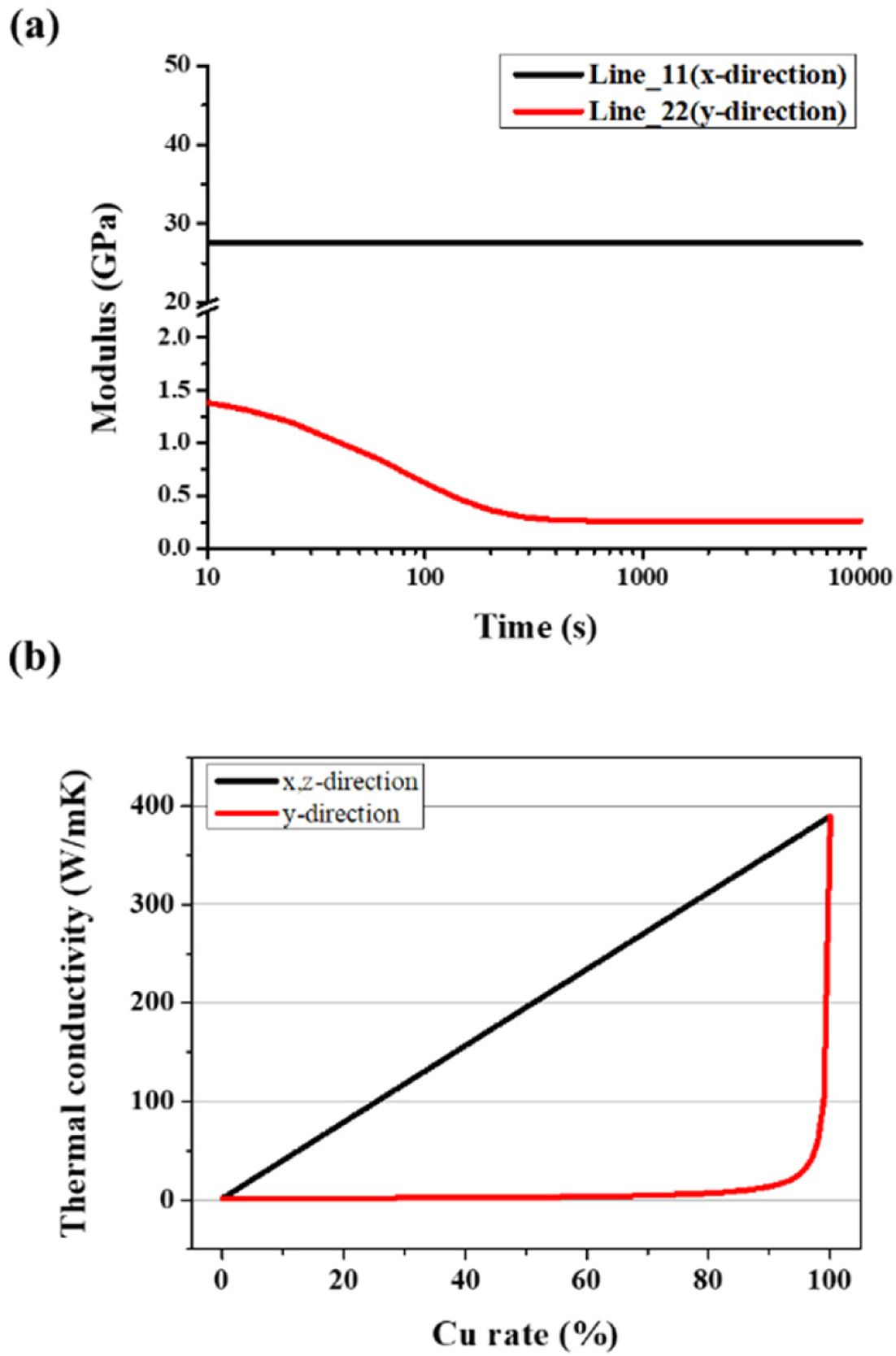

Fig. 6(a)는 이방성 유효 기계적 거동을 구체적으로 보여준다. 전체적으로 y-방향(Line_22)이 x-방향(Line_11)에 비해 낮은 강성을 가지며, 이후 점차적으로 수렴하는 비선형 특성을 나타낸다. 이는 y-방향은 Cu 배선이 수직 형태로 배치되어 있어 하중이 작용되었을 때 절연재 내부에서 점탄성에 의한 응력 이완이 지배적으로 발생함을 의미한다. 반면 x-방향은 구리 배선과 평행하게 배열되어 점탄성에 의한 응력 이완보다 선형적 탄성 물성이 지배적이기 때문에 y-방향보다 점탄성에 의한 영향이 적은 것이 관찰되었다.

열은 전도도가 낮은 절연체 보다 전도도가 높은 구리 배선을 통해 주로 이동한다. 앞서 제시된 열 저항 모델을 통해 계산된 방향별 유효 열 전도도는 아래 식과 같다.

Fig. 6(b)는 열 저항 모델을 기반으로한 이방성 열전도도 결과를 보여준다. 도출된 유효 열 전도도 계산 결과는 방향에 따라 열 확산 속도가 다르다는 것을 보여준다. x-방향으로는 Cu 배선이 연속적으로 배열되어 있어 열이 배선을 따라 빠르게 전달되고, 이에 따라 높은 열 전도도가 도출되었다. 반면, y-방향으로는 절연체가 반복적으로 존재하므로 열 흐름이 흐름이 제한되어 낮은 열 전도도가 도출되었다.

4.2 이방성 열-기계 특성 고려 해석 및 실험 검증

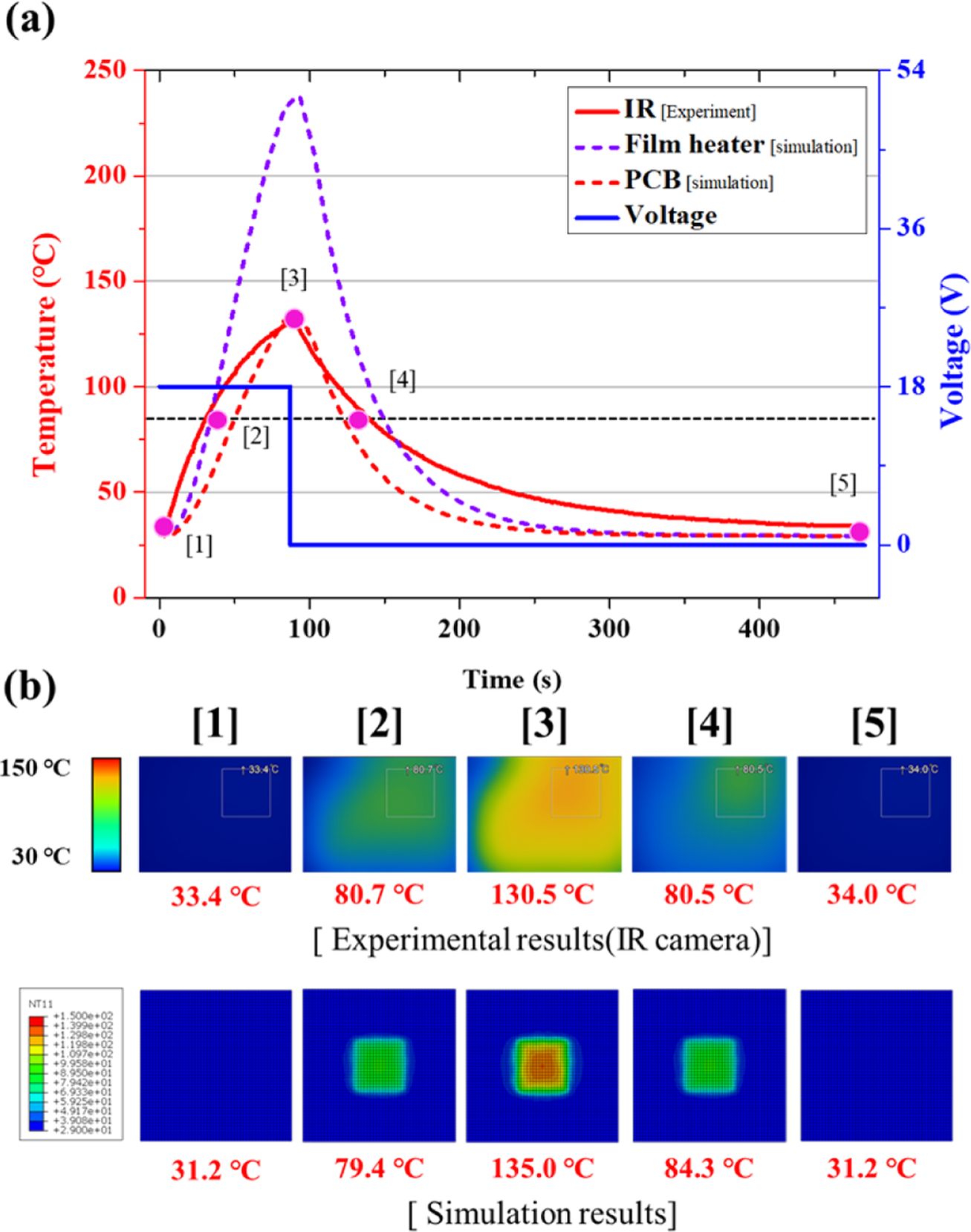

IR 카메라로 측정한 열응답 결과는 Fig. 7과 같으며, 18 V를 90초 동안 인가하였을 때 film heater 부착 반대면에서 약 130oC 수준의 최대 온도가 관찰되었다. 초기 시작 온도는 약 33.4oC였으며, 실험은 상온(23oC) 조건에서 수행되었다. 전원 인가를 해제한 이후 자연 대류(air cooling)에 의해 온도는 점진적으로 감소하였으며, 약 380초 경과 시 초기 조건과 유사한 약 34oC로 복귀하는 것이 확인되었다. 이러한 가열–냉각 과정을 총 6회 반복하여 온도 응답 거동을 계측하였다. 시간에 따른 온도 변화 곡선에서 전압 인가 직후 급격한 온도 상승이 발생하였으며, 최대 온도 도달 이후 전원 차단 시 지수 감쇠 형태의 냉각 거동이 관찰되었다. 반복 사이클 동안 최대 온도 및 냉각 특성은 큰 변화 없이 안정적으로 재현되었으며, 이는 열 전달 거동이 반복 하중 조건에서도 일관되게 유지됨을 의미한다. 실험–해석 비교 결과, IR 카메라로 측정된 표면 온도와 Joule heating을 기반으로 예측된 해석 온도는 전반적으로 유사한 경향이 관찰되었다.

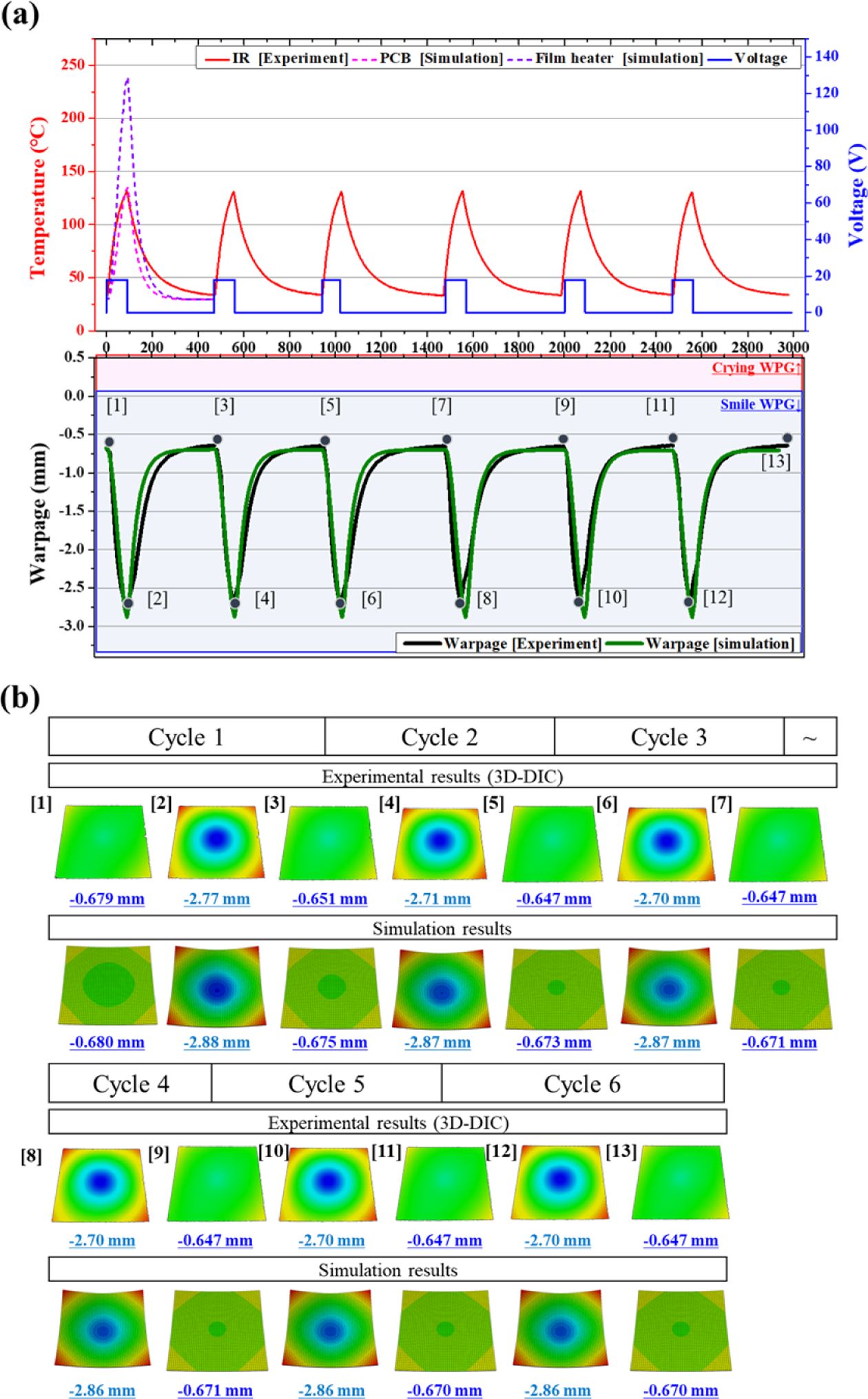

Fig. 8에서 나타나듯 3D-DIC를 활용한 워피지(WPG) 측정 결과, 초기 상태에서 약 0.679 mm 수준의 smile 형상의 초기 워피지가 관찰되었다. 첫 번째 사이클에서 승온이 진행됨에 따라 워피지는 심화되어 약 2.77 mm 수준까지 증가하였다. 이는 층간 온도 불균일성 및 열-기계 물성 차이에 의한 결과이다. 그러나 Joule heating에 의한 발열–냉각 사이클이 반복됨에 따라, 상온 및 고온 조건에서의 워피지는 점차 완화되는 경향을 보였다.

특히 약 3번째 사이클까지 PCB 내 폴리머 기반 절연층(PPG)의 점탄성 거동에 의해 응력 이완(stress relaxation)이 발생하며 최대 워피지가 감소하는 것이 확인되었다. 이는 시간 및 온도 의존적 점탄성 특성에 의해 열 사이클 동안 축적된 열-기계 응력이 부분적으로 완화되었기 때문으로 판단된다. 4번째 사이클 이후에는 열 이력이 반복됨에도 불구하고 최대 약 2.7 mm 수준의 smile 워피지가 유지되었으며, 상온에서는 약 0.647 mm 수준의 워피지가 안정적으로 유지되는 경향이 관찰되었다. 이는 점탄성 완화가 일정 수준에 도달한 이후 준안정 상태에 수렴하였기 때문이다. 실험–해석 비교 결과에서도 3D-DIC로 측정된 워피지 변화 양상과 유사하게, 해석 모델에 적용된 PPG의 점탄성 및 회로층의 이방성 점탄성 특성에 의해 워피지가 점차 완화되는 경향이 재현되었다. 특히 3번째 사이클까지 상대적으로 큰 완화가 나타났으며, 이후 사이클에서는 워피지 심화 및 유지 거동이 실험과 유사하게 나타났다.

|

Fig. 6 Results of effective anisotropic thermo-mechanical properties; a) Anisotropic viscoelastic and b) Anisotropic thermal properties |

|

Fig. 7 Comparison of temperature results of (a) simulation and (b) experimental results from IR camera |

|

Fig. 8 Comparison of warpage behavior of (a) simulation and (b) experimental results from IR camera |

본 연구에서는 회로 패턴의 이방성 점탄성 특성과 열전도도의 방향성을 고려한 등가화 기법을 통해, 반도체 패키지의 작동 중 워피지(Warpage) 거동을 정밀하게 예측할 수 있는 해석 기법을 제시하였다. 고해상도 회로 이미지 처리 기반으로 패턴의 배선 방향성과 밀도를 정량화하고, 이를 통해 도출된 이방성 기계적 및 열 물성은 유한요소해석(FE)에 반영되었다. 이를 통해, 반도체 패키지 내에서 발생하는 열-기계 연성 거동을 시뮬레이션을 통해 분석하고, 열 사이클에 따른 워피지 형성 메커니즘을 고찰하였다.

This research was supported by the Nano & Material Technology Development Program through the National Research Foundation of Korea(NRF) funded by Ministry of Science and ICT(RS-2024-00428299). This work was supported by the Korea Planning and Evaluation Institute of Industrial Technology (KEIT) and Ministry of Trade, Industry, and Energy (MOTIE) of the Republic of Korea (RS-2024-00418263). This work was supported by Korea Institute of Energy Technology Evaluation and Planning (KETEP) grant funded by the Korea government (MOTIE) (20212020800090, Development and Demonstration of Energy-Efficiency Enhanced Technology for Temperature-Controlled Transportation and Logistics Center).

- 1. C.-T. Ko, and K.-N. Chen, “Reliability of key technologies in 3D integration,” Microelectronics Reliability, Vol. 53, No. 1, pp. 7-16, 2013.

-

- 2. X. Dai, Y. Wang, Y. Wu, H. Luo, G. Liu, D. Li, and S. Jones, “Reliability design of direct liquid cooled power semiconductor module for hybrid and electric vehicles,” Microelectronics Reliability, Vol. 64, pp. 474-478, 2016.

-

- 3. A. Ahmad, “Automotive semiconductor industry-trends, safety and security challenges,” 2020, pp. 1373-1377.

-

- 4. J. Meza, T. Xu, K. Veeraraghavan, and O. Mutlu, “A large scale study of data center network reliability,” 2018, pp. 393-407.

-

- 5. J. McPherson, “Brief history of JEDEC qualification standards for silicon technology and their applicability (?) to WBG semiconductors,” 2018, pp. 3B. 1-1-3B. 1-8.

-

- 6. J. Canny, “A computational approach to edge detection,” IEEE Transactions on Pattern Analysis and Machine Intelligence, No. 6, pp. 679-698, 1986.

-

- 7. N. Dalal and B. Triggs, “Histograms of oriented gradients for human detection,” 2005, pp. 886-893.

-

- 8. S.-J. Joo, B. Park, D.-H. Kim, D.O. Kwak, J. Park, and H.S. Kim, “Bi-directional homogenization equivalent modeling for the prediction of thermo-mechanical properties of a multi-layered printed circuit board (PCB),” Journal of Micromechanics and Microengineering, Vol. 26, No. 4, pp. 045006, 2016.

-

This Article

This Article

-

2026; 39(1): 60-66

Published on Feb 28, 2026

- 10.7234/composres.2026.39.1.060

- Received on Jun 13, 2025

- Revised on Jul 25, 2025

- Accepted on Feb 27, 2026

Services

Services

Shared

Correspondence to

Correspondence to

- Hak-Sung Kim

-

* Department of Mechanical Convergence Engineering, Hanyang University, Seoul, Republic of Korea

** Hanyang Research Center for Advanced Semiconductor Packaging, Hanyang University - E-mail: kima@hanyang.ac.kr

Copyright ⓒ The Korean Society for Composite Materials. All rights reserved.

Copyright ⓒ The Korean Society for Composite Materials. All rights reserved.